Although 5G deployments have started, many challenges are ahead for both operators and platform vendors.

5G DIVERSE USE CASES AND EVOLVING STANDARDS

To understand the challenges, it is instructive to compare 4G to 5G use cases. 4G has one main use case: mobile data.

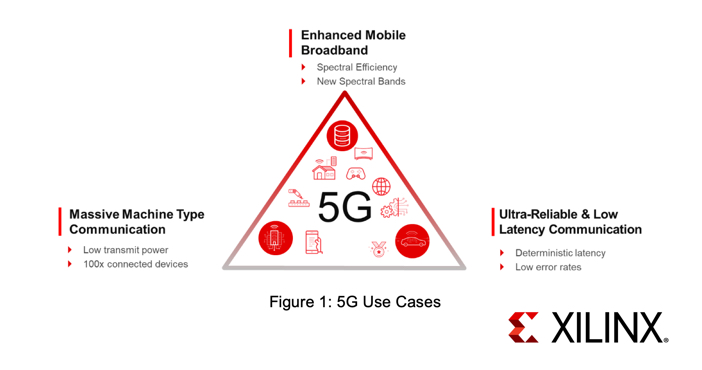

5G, on the other hand, has three main use cases as shown in Figure 1: enhanced Mobile Broadband (eMBB), Ultra-Reliable Low-Latency Communication (URLLC), and massive Machine Type Communication (mMTC). The eMBB use case provides data rates up to 100X faster and is the use case promoted today. The URLLC use case can provide up to 10X reduction in latency while the mMTC increases the number of connected devices by 100X. If each use case were optimized separately, it would lead to very different radio solutions; 5G blends them into one standard. A flexible radio platform is needed to support these diverse use cases.

Figure 1: 5G Use Cases

The 5G standard will evolve over the next decade. New features that we do not know about today will be incorporated to meet market needs. Hardware providers need a solution that can adapt with the 5G evolution. FPGAs, with programmable logic, are the best solution to meet diverse and evolving requirements but are not as power efficient as ASIC implementations.

ZYNQ RFSOC DFE MEETS CURRENT AND FUTURE 5G NEEDS

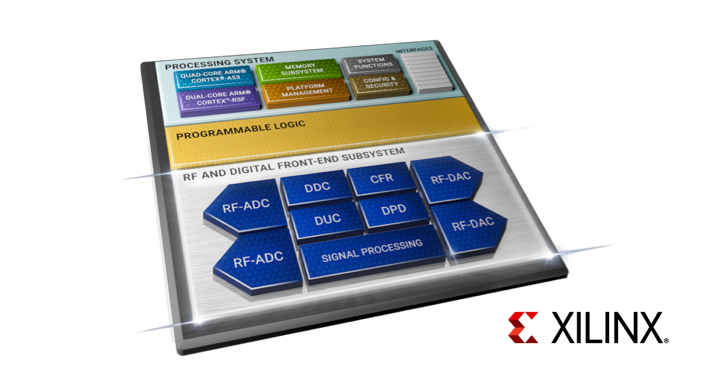

To meet these challenges, Xilinx has introduced the Zynq® RFSoC DFE (Digital Front-End), a new, innovative product that can adapt and scale with 5G while addressing the performance, cost, and power challenges of widespread deployments. See Figure 2.

Figure 2: Zynq RFSoC DFE Integrates a Complete DFE Subsystem with Hard IP

The Zynq RFSoC DFE implements known and compute-intensive DFE functions in a hardened core (an ASIC-like structure), which is configurable for both 4G and 5G NR standards.

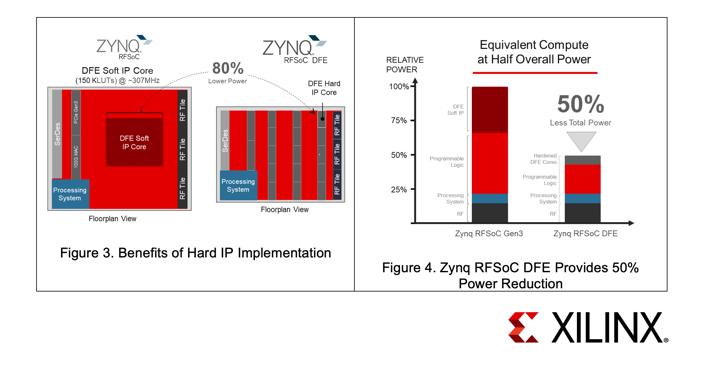

These hardened cores reduce power consumption by up to 80% compared to traditional FPGA soft logic as shown in Figure 3. When fully utilizing the DFE hard IP blocks, the total power consumption of a Zynq RFSoC DFE device is about 50% lower than an equivalent implementation in a Zynq RFSoC Gen 3 device as shown in Figure 4.

In addition to the hard DFE IP blocks, the Zynq RFSoC DFE includes enough programable or soft logic to adapt to evolving 5G standards and diverse use cases, and is architected so that customers can bypass any IP core, or insert their own IP.

The Zynq RFSoC DFE offers 2X performance-per-watt compared to the third generation of Zynq RFSoC and scales from small cell to massive MIMO (mMIMO) macrocells. It is the industry’s only direct RF platform with 400 MHz of instantaneous bandwidth enabling multi-mode, multi-band radios in all bands up to 7.125GHz.

The Xilinx Zynq RFSoC DFE, a new class of product, has more hard logic than soft, but remains adaptable to address evolving market requirements and customer needs. This innovative approach achieves the cost and power economies of an ASIC but retains the adaptability of an FPGA solution.

Learn more about the breakthrough Zynq RFSoC DFE at Xilinx Adapt: 5G, a 2-day virtual technical event from November 18-19. Join us to hear about the latest wireless solutions from Xilinx, along with sessions on key industry trends and how to stay ahead of the 5G deployment curve. Register here:

More information on the entire family of Zynq® UltraScale+ RFSoCs can be found at: www.xilinx.com/rfsoc-dfe

RFSoCs can be found at: www.xilinx.com/rfsoc-dfe

The post 5G diverse use cases and evolving standards appeared first on RCR Wireless News.